For the development of FPGA technology, the acquisition of Xilinx and Altera by AMD and Intel respectively is obviously an important turning point in this history. With the FPGA company changing from an independent company to a sub department of the chip giant, its technology development strategy will also change greatly. This paper will make a prospect for the development of this strategy.

First of all, with the integration with chip giants, FPGA will be further integrated with traditional chips to give full play to its programmable advantages to enable new capabilities of traditional chips and even realize new chip categories.

New types of FPGA enabled chips

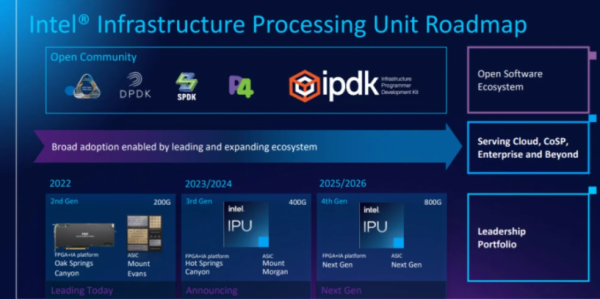

For Intel, an example of such a new category of chips is IPU (infrastructure processing unit). With the extensive use of the data center, some important tasks in the data center, including network control, storage management and network security, also have an increasing demand for processing capacity. With the major chip companies launching their own solutions, Intel has also launched IPU for this market. Last month, Intel just released its roadmap for the future of IPU, in which we see that IPU in the future up to 2026 will include two versions, one is a high-performance version based on ASIC, and the other is a programmable version based on FPGA (including oak springs Canyon in 2022, hot springs Canyon in 2023/2024, and the version under planning in 2025/2026). Among them, the IPU based on FPGA version is actually an acceleration card integrating Intel FPGA chip and Intel Xeon CPU. It can handle various network, storage and security protocols in a flexible way, so as to ensure maximum programmability without worrying about compatibility.

In fact, for FPGA solutions similar to data center storage and network, there have been startups engaged in related projects in the past few years. However, with the admission of giant Intel, we believe that such fpga+cpu solutions will really become one of the mainstream solutions. The fact that the start-up companies are engaged in relevant projects and obtain financing shows that the technical direction is feasible, and Intel's entry into this market has brought ecological resources that the start-up companies do not have. We believe that in the next few years, FPGA and CPU will be more closely integrated (for example, chiplet), so as to truly turn the flexible and programmable IPU into a new chip category enabled by FPGA.

Coincidentally, AMD is also actively planning to integrate Xilinx's FPGA and AMD's CPU - at AMD's earnings conference in May, CEO Lisa Su announced that she would release a CPU integrated with Xilinx AI engine in 2023, that is, a CPU with powerful AI computing power. Up to now, AI related computing has been performed in GPU or other dedicated acceleration hardware. Intel's previous efforts to optimize AI running on CPU have not been widely recognized by the market, as long as the number of CPU computing units is limited. However, since the overall AI task is not only a neural network, but also other parts of the program execution run on the CPU, if the CPU and AI acceleration unit can be closely coupled, the overall performance of the task will be improved. This is also estimated to be the original intention of AMD to propose a CPU integrated with FPGA AI engine, and this is also an example of a new chip category enabled by FPGA.

To sum up, with the further popularization of tasks such as data centers and artificial intelligence, giants such as Intel and AMD will consider how to make full use of the flexibility of FPGA to deal with these markets. In the current situation, it is not the best solution to launch FPGA products, but to launch new chip categories by integrating FPGA and other chips, which will be an important market direction for FPGA in the future, Next, we will also predict the most critical breakthrough point of FPGA in the future from the technical direction.

Stronger integration and connectivity

As mentioned above, as FPGA needs to play a key role in enabling new chip systems, we believe that integration and interconnection have become an important technical key point. The integration and interconnection here include two levels: first, at the FPGA level, we believe that the FPGA chip itself will integrate more and more related IPS, so as to make the FPGA chip more functional and efficient; The other level is the integration of FPGA and other chips in the system. We believe that chipet and other advanced packaging technologies and related interconnection technologies will be the core.

First of all, at the FPGA chip level, FPGA provides flexibility, but it is inefficient for general modules (such as processors). Therefore, integrating hard IP on FPGA chip to meet the requirements of efficiency and flexibility will continue to be the mainstream idea, and the number of integrated IP will be more and more in the future. On the same chip, FPGA is used as the core module, and other hard IP modules (such as CPU, Ethernet, video codec and memory control) are carried at the same time. NOC and other on-chip interconnection schemes are used to connect FPGA and other IPS. Amd/xilinx is a pioneer in this field. It can be seen from the versal product wiring diagram that more and more hard IP will be integrated on the chip, and Intel's FPGA will have a similar design in this regard. By integrating these hard IPS, FPGA will be able to provide more functions. For Xilinx, the most critical IP is AI related DSP, and we have also seen some new IP, such as direct RF, which can directly support RF applications through ultra-high rate digital to analog conversion, and is expected to be combined with FPGA to meet various wireless communication requirements. In this way, real software radio can be realized, thus opening new application scenarios for FPGA. Therefore, integrating more and more hard IP on FPGA chip will become an important technical path to further strengthen the FPGA function and enter new application scenarios.

The second level is the integration and interconnection of FPGA and other chips at the system level. We believe that such integration will be the key for FPGA to enable new chip systems and categories. Combined with the more hard IP integration on FPGA chips mentioned earlier, we believe that FPGA with more and more powerful functions can enable more and more new chip categories and open the market. At this level, we believe that the most critical technology path is to realize flexible and customizable heterogeneous integration in the form of advanced packaging, supplemented by innovative interconnection technologies. In this regard, Intel earlier released the use of advanced packaging technology (emib) to integrate FPGA, high-speed transceiver (for data center scalability interconnection) and DRAM into one package. At the hotchips conference later this year, Intel also had a report on using heterogeneous integration to realize innovative RF applications. The main advantage of heterogeneous integration lies in its flexibility. For example, it can be integrated with different types and specifications of chips according to the needs of users, so as to maximize the trade-off between performance, cost and customization.

Similarly, amd plans to integrate Xilinx FGPA and CPU. Although no specific technical parameters have been released at present, we believe that chiplet technology may also be used according to AMD's previous investment in chipet and AMD's previous relevant patents.

As the scale of such integration becomes larger and larger, the demand for interconnection becomes higher and higher. Otherwise, interconnection may become a bottleneck in multi chip systems. Interconnection not only needs to provide high bandwidth, but also needs to support important system level functions, such as cache and memory consistency. At present, both Intel and AMD's FPGAs support the relevant CXL protocol. We believe that with the larger scale integration between FPGAs, processors and other chips, more and more complex and high-speed inter chip interconnection will become a key technology.

Software will be key

In addition to hardware, how to make the most efficient use of FPGA in practical tasks is also an extremely critical issue. As FPGA and other chips (such as CPU) are closely integrated to form a heterogeneous chip system, how to ensure that the software can make full use of FPGA and avoid scheduling bottlenecks is a very complex but important problem. This is a highly challenging problem, because the programming model of FPGA and other parts of the system (such as CPU) may be very different. Therefore, how to ensure that the software can correctly divide tasks (that is, assign tasks suitable for FPGA to FPGA and tasks suitable for other processors to corresponding processors), reasonably handle scheduling and memory management, and provide a user-friendly form for software engineers, It's a big project. These tasks are quite different from traditional FPGA Software (i.e. mainly for front-end and back-end logic synthesis tasks).

In this field, Intel and AMD are actively investing. For example, on the IPU roadmap released by Intel, open and flexible software ecology is an important investment area of Intel. Correspondingly, Intel just announced that it would acquire codeplay, a cross platform heterogeneous chip software compiler. This move is also considered by the industry as an investment in the next generation FPGA Software. At the same time, amd also said at the financial report conference in May that it would vigorously invest in the software field, which obviously also includes FPGA related software research and development. We believe that as FPGA becomes an important part of the new chip system, the corresponding software ecology must also keep up, so as to make such a new paradigm of FPGA system truly enter the mainstream.

Article From:http://rcbscable.com/15.html

Media Contact

Company Name: MFMIC Technology Company Limited

Email: Send Email

Phone: 83741556

Address:Rm 602, 6/F, Wayson Comm Bldg, 28 Connaught West

Country: HongKong

Website: https://www.mfmic.com/